Les différences fondamentales entre les logiques CMOS et TTL incluent des composants CMOS plus chers, des circuits CMOS ne consommant pas autant d'énergie et une consommation d'énergie TTL augmentant plus lentement. D'autres différences incluent la transmission de signaux numériques et les dommages susceptibilité.

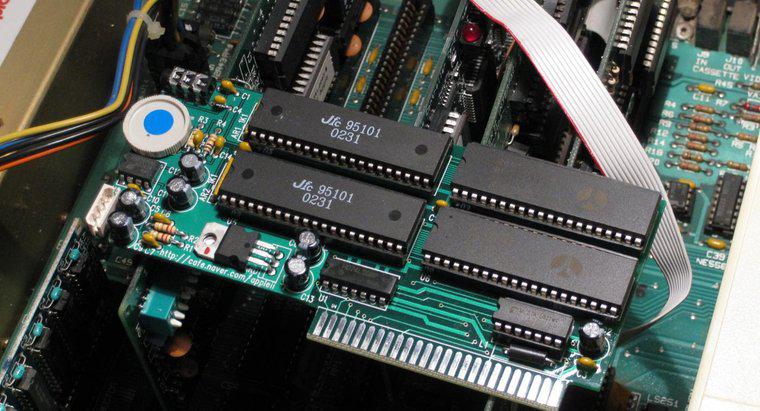

Les composants TTL sont généralement moins chers que les composants CMOS. Cependant, en raison de puces plus petites, CMOS est généralement moins cher au niveau du système. Au repos, les circuits CMOS ne consomment pas autant d'énergie que les circuits TTL. Cependant, des vitesses d'horloge plus élevées entraînent une augmentation de la consommation d'énergie CMOS à un rythme plus rapide que TTL. Les composants CMOS sont plus susceptibles d'être endommagés par les décharges électrostatiques que les composants TTL. Les signaux numériques sont plus économiques et plus simples avec les puces CMOS en raison des temps de montée et de descente plus longs.

La dissipation de puissance de CMOS est généralement de 10 nW par porte tandis que la dissipation de puissance de TTL est typiquement de 10 mW par porte. Les délais de propagation de TTL sont généralement de 10 nS tandis que les délais de propagation de CMOS sont généralement compris entre 25 nS et 50 nS.

La plage de niveau de tension pour TTL est généralement de 4,75 V à 5,25 V. La plage de niveaux de tension pour CMOS va de 0 à 1/3 VDD à un niveau bas et de 2/3 VDD à VDD à un niveau élevé.